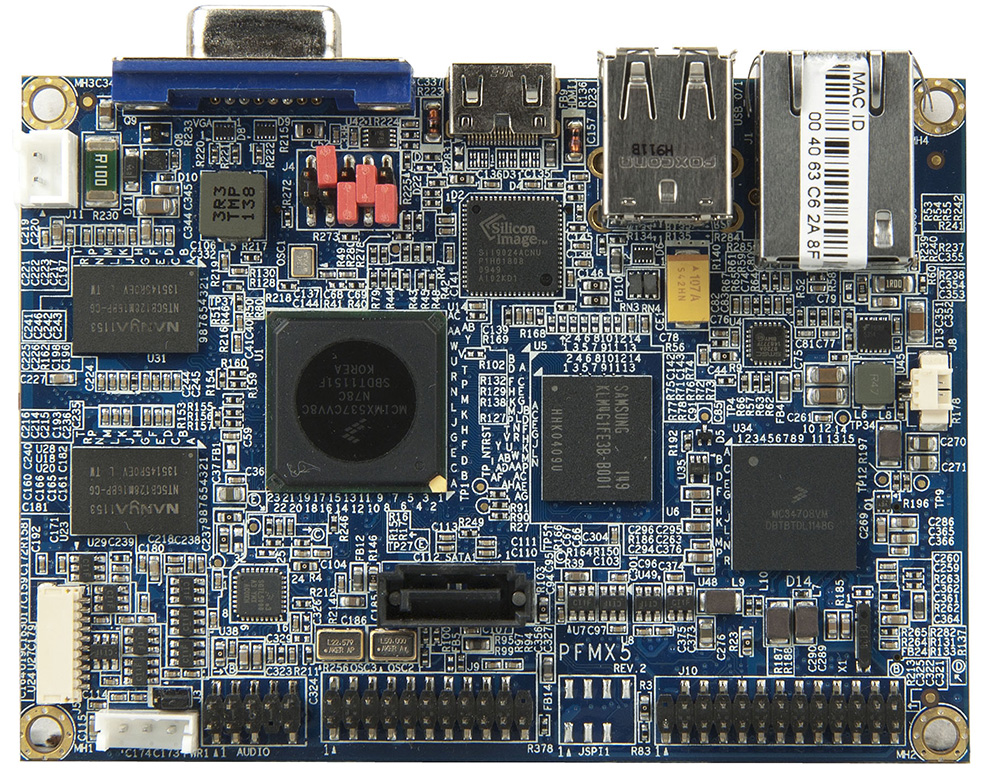

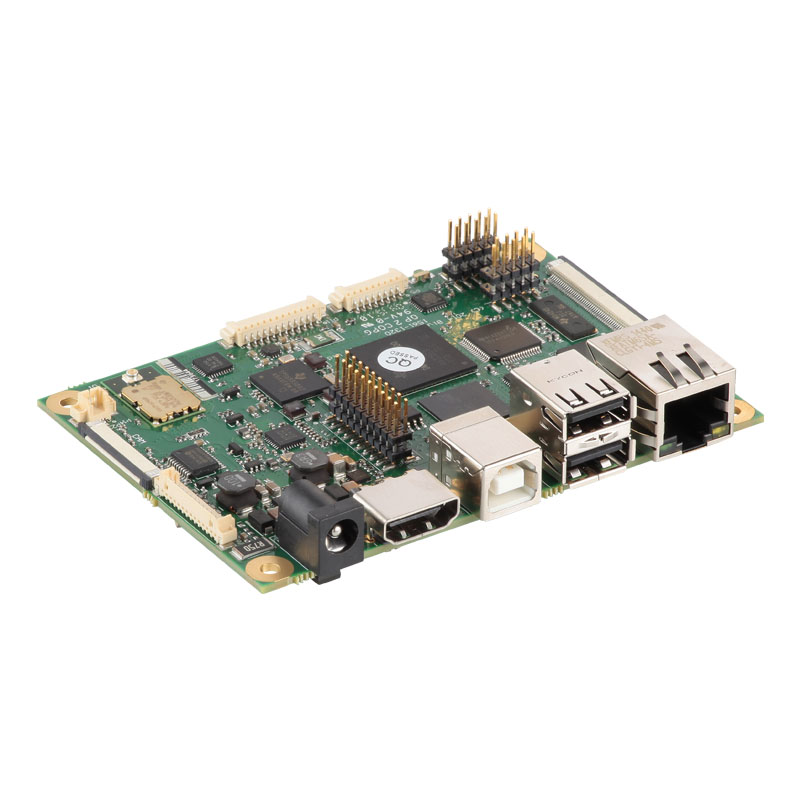

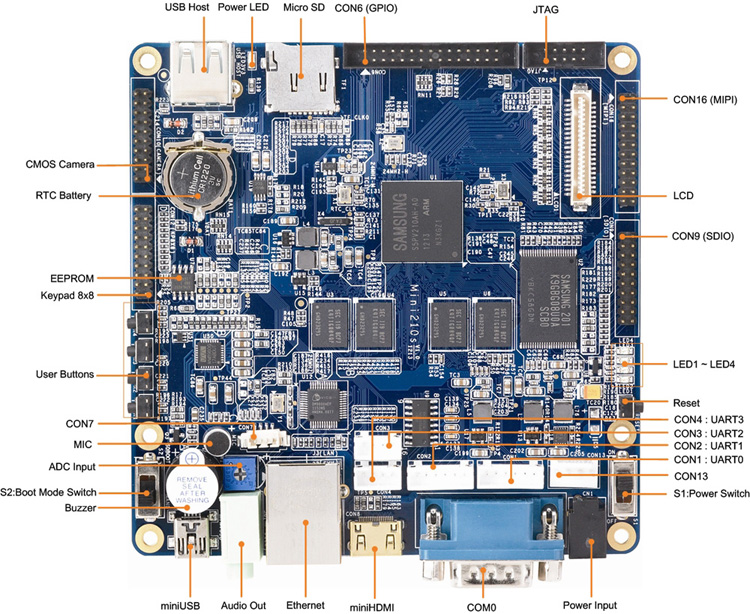

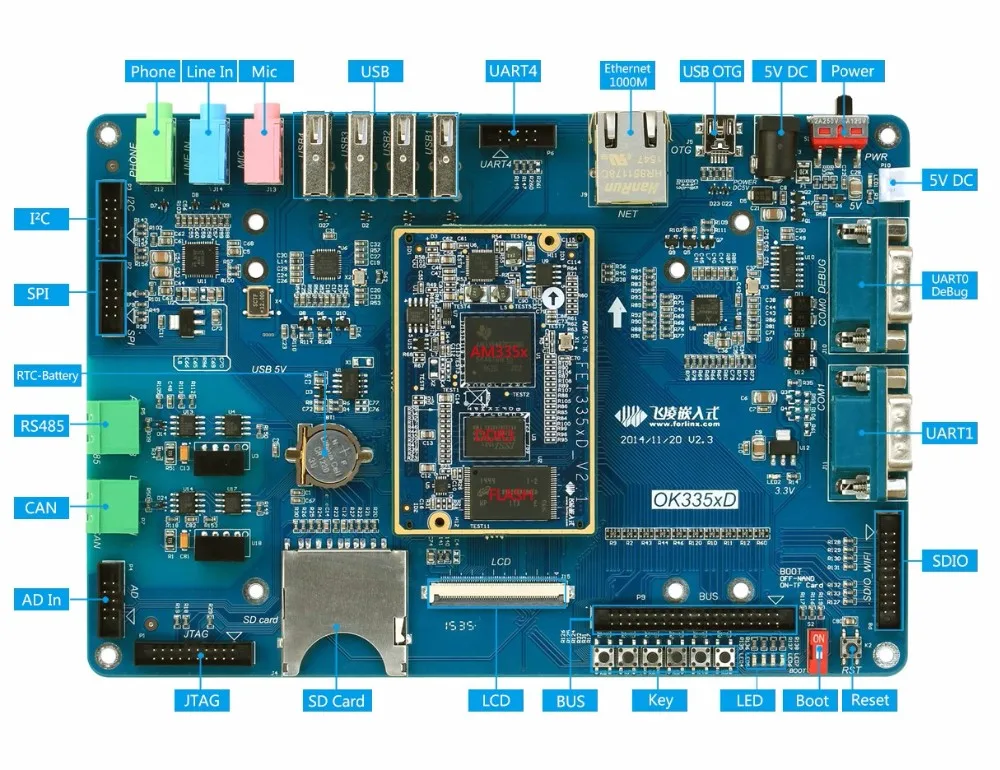

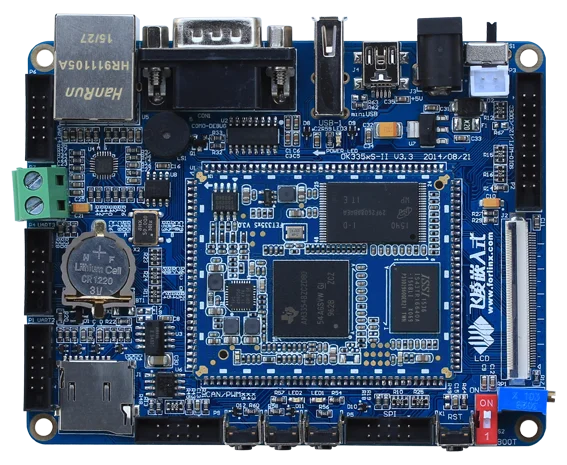

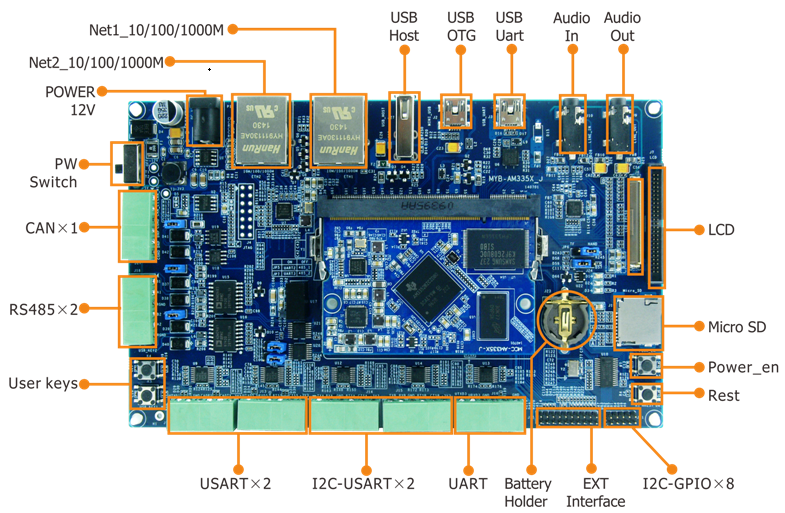

The SRG-3352C MQTT Gateway is powered by the Arm® Cortex-A8 800 MHz RISC processor. This innovative processor allows the system to enable energy efficient Industrial IoT deployments, even allowing the system to be deployed with solar or battery power. With low thermal output, the system can operate in a wide range of temperatures from 0°C up to 60°C without a loss in performance.

The SRG-3352C provides reliable and cost-effective edge gateway operations, with low upfront cost and reduced maintenance requirements overtime. To connect from edge to cloud, the SRG-3352C supports 3G/4G LTE as well as NB-IoT to help reduce carrier costs.

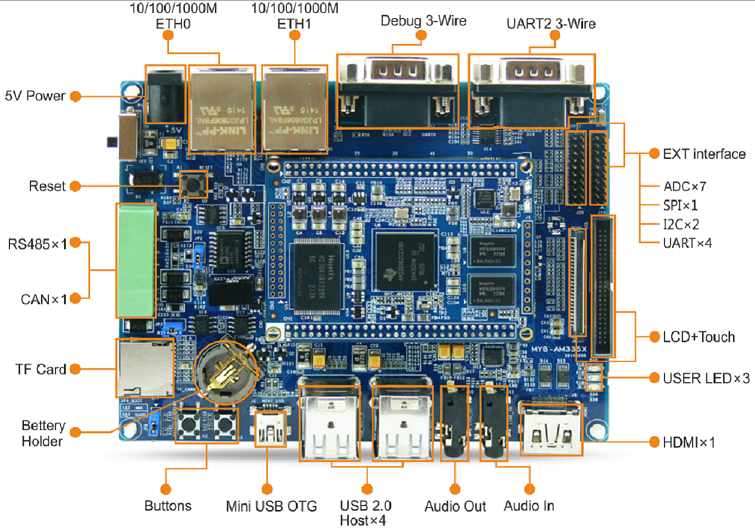

The SRG-3352C helps get your Industrial IoT project up and running quickly, with pre-installed Modbus and MQTT libraries. The system also features an onboard Wi-Fi and Bluetooth module to support wireless network deployments, and comes with a broad I/O layout including two Gigabit Ethernet ports, USB 2. 0 and RS-485 ports. Optional wall-mount and DIN rail kits ensure the SRG-3352C can be deployed anywhere it’s needed. The SRG-3352C is also compatible with popular cloud services including AWS, Azure, and Arm Pelion, or can be configured to work with a customer’s own cloud platform.

0 and RS-485 ports. Optional wall-mount and DIN rail kits ensure the SRG-3352C can be deployed anywhere it’s needed. The SRG-3352C is also compatible with popular cloud services including AWS, Azure, and Arm Pelion, or can be configured to work with a customer’s own cloud platform.

| system | |

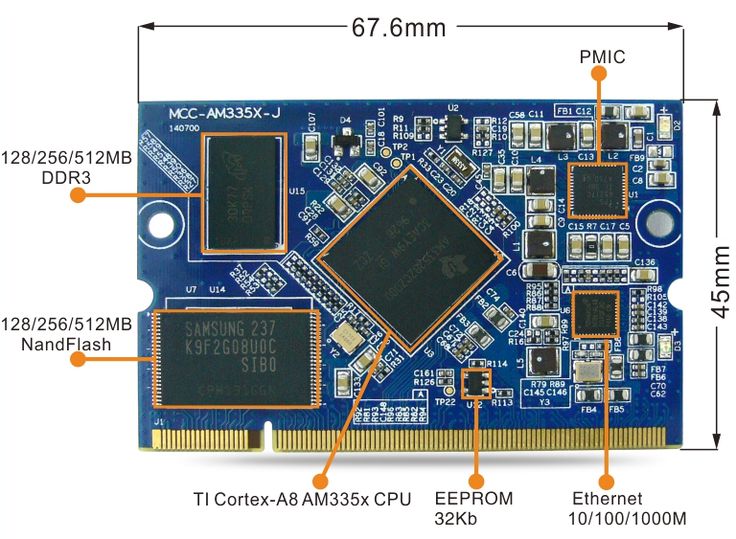

| processor | ARM Cortex-A8 800 MHz RISC Processor |

| Memory | Onboard DDR3L 1GB |

| Storage | eMMC 16GB |

| Real Time Clock | RTC, with 3V CR2032 Lithium battery x 1 |

| Security | — |

| Indicator | Programmable LED control x 4 |

| Cellular | Mini PCIe Connector x 1 |

| Wireless Lan | Onboard WiFi 802. 11 b/g/n, Bluetooth5.2 / BLE 11 b/g/n, Bluetooth5.2 / BLE |

| Operating System | Debian 10 |

| Support Protocol | Modbus / MQTT Library(by request) |

| i/o | |

| Serial Port | RS-485, DB9 Connector x 2 |

| Ethernet | Gigabit Ethernet, RJ-45 x 2 |

| USB | USB 2.0, Type A x 2 |

| ADC | — |

| DI/DO | — |

| Can Bus | — |

| Display | — |

| Power Connector | Lockable DC Jack |

| Debug Port | Micro USB x 1 |

| Expansion Slot | SIM card slot x 1 Micro SD slot x 1 |

| Other Interface | — |

| power supply | |

| Power Requirement | DC9-30V |

| Power Consumption | 3.36 W (Full Loading) |

| MTBF (hours) | 855590 |

| environmental and mechanical | |

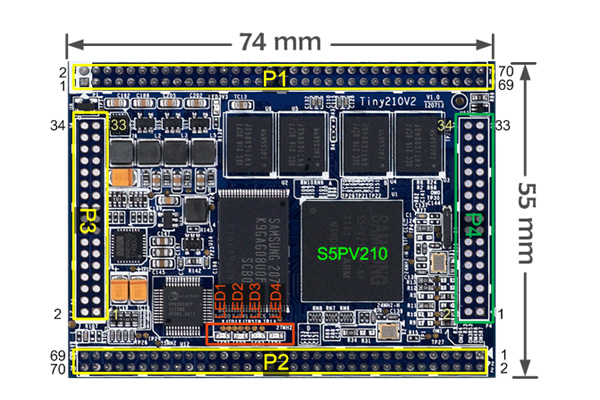

| Dimension | 4. 3” x 4.33” x 1.54” (109 x 110 x 39 mm) 3” x 4.33” x 1.54” (109 x 110 x 39 mm) |

| Weight | 430 g |

| Mounting | Wallmount, Din Rail (Optional) |

| Operating Temperature | 32 °F ~ 140 °F (0 °C ~ 60 °C) |

| Storage Temperature | -40 °F ~ 176 °F (-40 °C ~ 80 °C) |

| Operating Humidity | 10% ~ 95% relative humidity, non-condensing |

| Part Number | |

|---|---|

| cpu | ARM Cortex-A8 800MHz |

| memory | Onboard DDR3L 1GB |

| thermal | Fanless |

| ports | RS-485 x 2 (DB9) |

| storage | eMMC 16GB, MicroSD x1 |

| lan | GbE x 2 |

| usb | USB 2.0 x 2 |

| expansion slot | Mini PCIe slot x 1, SIM card socket x 1 |

| power | DC 9-30V |

| operation temp | 0°C ~ 60°C @ 0. 5 m/s airflow 5 m/s airflow |

| others | 3G/4G LTE module (optional) |

| 1255300366 | Power Adapter. AC/DC. 100-240VAC. 12VDC/3A.36W. |

| 9741EG25G0 | PCIe mimi card. 4G LTE. module kit. Global Band W/SIM holder. W/Cable & antenna. Quectel. EG25-G |

| 9651352C02 | DIN rail kit. 47x25mm. SRG-3352C series |

| 9651352C01 | Wall mount kit. 110x26mm. SRG-3352C series |

смартфонывидеокартыбеспроводные наушникипроцессоры

46балла

Apple A8

9балла

ARM Cortex-A9

Победитель при сравнении

vs

58 фактов в сравнении

Apple A8

ARM Cortex-A9

Apple A8

vs

Apple A9

ARM Cortex-A9

vs

ARM Cortex-A53

Apple A8

vs

Apple A12 Bionic

ARM Cortex-A9

vs

ARM Cortex-A55

Apple A8

vs

Apple A8X

ARM Cortex-A9

vs

ARM Cortex-A7

Apple A8

vs

Apple A10

ARM Cortex-A9

vs

ARM Cortex-A72

Apple A8

vs

Qualcomm Snapdragon 625

ARM Cortex-A9

vs

ARM Cortex-A15

Apple A8

vs

Qualcomm Snapdragon 665

ARM Cortex-A9

vs

Qualcomm Snapdragon 855

Apple A8

vs

Qualcomm Snapdragon 450

ARM Cortex-A9

vs

Apple A12 Bionic

Apple A8

vs

Qualcomm Snapdragon 805

ARM Cortex-A9

vs

HiSilicon Kirin 659

Apple A8

vs

ARM Cortex-A15

ARM Cortex-A9

vs

MediaTek Helio P22

Apple A8

vs

MediaTek Helio G88

Apple A8

3 Отзывы пользователей

Apple A8

7. 3/10

3/10

3 Отзывы пользователей

ARM Cortex-A9

0 Отзывы пользователей

ARM Cortex-A9

0.0/10

0 Отзывы пользователей

Игры

5.7/10

3 votes

Отзывов пока нет

Производительность

7.0/10

3 votes

Отзывов пока нет

скорость центрального процессора

2 x 1.4GHz

Неизвестно. Помогите нам, предложите стоимость. (ARM Cortex-A9)

Скорость центрального процессора показывает сколько циклов обработки в секунду может выполнять процессор, учитывая все его ядра (процессоры). Она рассчитывается путем сложения тактовых частот каждого ядра или, в случае многоядерных процессоров, каждой группы ядер.

поток выполнения процессора

Неизвестно. Помогите нам, предложите стоимость. (ARM Cortex-A9)

Большее число потоков приводит к более высокой производительности и лучшему одновременному выполнению нескольких задач.

Использует технологию big.LITTLE

✖Apple A8

✖ARM Cortex-A9

Используя технологию big.LITTLE, чип может переключаться между двумя наборами процессоров, чтобы обеспечить максимальную производительность и срок службы батареи. Например, во время игр более мощный процессор будет использоваться для повышения производительности, в то время как проверка электронной почты будет использовать менее мощный процессор для продления срока службы аккумулятора.

Использует HMP

✖Apple A8

✖ARM Cortex-A9

HMP — это более продвинутая версия технологии big.LITTLE. В этой конфигурации, процессор может использовать все ядра одновременно, или только одно ядро для задач низкой интенсивности. Это может обеспечить высокую производительность и увеличение срока службы батареи соответственно.

скорость турбо тактовой частоты

Неизвестно. Помогите нам, предложите стоимость. (Apple A8)

(Apple A8)

Неизвестно. Помогите нам, предложите стоимость. (ARM Cortex-A9)

Когда процессор работает ниже своих ограничений, он может перейти на более высокую тактовую частоту, чтобы увеличить производительность.

Кэш L2

Неизвестно. Помогите нам, предложите стоимость. (Apple A8)

Неизвестно. Помогите нам, предложите стоимость. (ARM Cortex-A9)

Больше сверхоперативной памяти L2 приводит к быстрым результатам в центральном процессорном устройстве и настройках производительности системы.

L1 кэш

Неизвестно. Помогите нам, предложите стоимость. (Apple A8)

Неизвестно. Помогите нам, предложите стоимость. (ARM Cortex-A9)

Больше сверхоперативной памяти L1 приводит к быстрым результатам в центральном процессорном устройстве и настройках производительности системы.

часовой множитель

Неизвестно. Помогите нам, предложите стоимость. (Apple A8)

Неизвестно. Помогите нам, предложите стоимость. (ARM Cortex-A9)

Помогите нам, предложите стоимость. (ARM Cortex-A9)

Часовой множитель контролирует скорость процессора.

L3 кэш

Неизвестно. Помогите нам, предложите стоимость. (Apple A8)

Неизвестно. Помогите нам, предложите стоимость. (ARM Cortex-A9)

Больше сверхоперативной памяти L3 приводит к быстрым результатам в центральном процессорном устройстве и настройках производительности системы.

скорость оперативной памяти

Неизвестно. Помогите нам, предложите стоимость. (Apple A8)

Неизвестно. Помогите нам, предложите стоимость. (ARM Cortex-A9)

Может поддерживать более быструю память, которая ускоряет производительность системы.

версия памяти DDR

Неизвестно. Помогите нам, предложите стоимость. (Apple A8)

Неизвестно. Помогите нам, предложите стоимость. (ARM Cortex-A9)

Память DDR (синхронная динамическая память с произвольным доступом и удвоенной скоростью передачи данных) является наиболее распространенным типом оперативной памяти. Новые версии памяти DDR поддерживают более высокие максимальные скорости и более энергетически эффективны.

Новые версии памяти DDR поддерживают более высокие максимальные скорости и более энергетически эффективны.

максимальный объем памяти

Неизвестно. Помогите нам, предложите стоимость. (Apple A8)

Неизвестно. Помогите нам, предложите стоимость. (ARM Cortex-A9)

Максимальный объем памяти (RAM).

максимальная пропускная способность памяти

Неизвестно. Помогите нам, предложите стоимость. (Apple A8)

Неизвестно. Помогите нам, предложите стоимость. (ARM Cortex-A9)

Это максимальная скорость, с которой данные могут быть считаны или сохранены в памяти.

каналы памяти

Неизвестно. Помогите нам, предложите стоимость. (ARM Cortex-A9)

Большее количество каналов памяти увеличивает скорость передачи данных между памятью и процессором.

версия eMMC

Неизвестно. Помогите нам, предложите стоимость. (Apple A8)

Неизвестно. Помогите нам, предложите стоимость. (ARM Cortex-A9)

Помогите нам, предложите стоимость. (ARM Cortex-A9)

Более новая версия еММС — встроенная флэш-карта памяти — ускоряет интерфейс памяти, оказывает положительное влияние на производительность устройства, например, при передаче файлов с компьютера на внутреннюю память через USB.

Поддерживает код устраения ошибок памяти

✖Apple A8

✖ARM Cortex-A9

Код устранения ошибок памяти может обнаружить и исправить повреждения данных. Он используется, когда это необходимо, чтобы избежать искажений, например в научных вычислениях или при запуске сервера.

Имеет встроенный LTE

✔Apple A8

✖ARM Cortex-A9

Система на чипе (SoC) имеет встроенный LTE сотового чипа. LTE может загружаться на более высоких скоростях, чем старые, технологии 3G.

скорость загрузки

Неизвестно. Помогите нам, предложите стоимость. (Apple A8)

Неизвестно. Помогите нам, предложите стоимость. (ARM Cortex-A9)

(ARM Cortex-A9)

Скорость загрузки — это измерение пропускной способности интернет-соединения, представляющее максимальную скорость передачи данных, с которой устройство может получить доступ к онлайн-контенту.

скорость загрузки

Неизвестно. Помогите нам, предложите стоимость. (Apple A8)

Неизвестно. Помогите нам, предложите стоимость. (ARM Cortex-A9)

Скорость загрузки — это измерение пропускной способности интернет-соединения, представляющее максимальную скорость передачи данных, при которой устройство может отправлять информацию на сервер или другое устройство.

Имеет TrustZone

✔Apple A8 (Apple Cyclone)

✔ARM Cortex-A9

Технология интегрирована в процессор для обеспечения безопасности устройства при использовании таких функций, как мобильные платежи и потокового видео с помощью технологии управления цифровыми правами (DRM).

использует многопоточность

✖Apple A8

✖ARM Cortex-A9

Технология многопоточности (такая как, Hyperthreading от Intel или Simultaneous Multithreading от AMD) обеспечивает более высокую производительность за счет разделения каждого физического ядра процессора на логические ядра, также известные как потоки. Таким образом, каждое ядро может запускать два потока команд одновременно.

Таким образом, каждое ядро может запускать два потока команд одновременно.

Имеет NX бит

✔Apple A8 (Apple Cyclone)

✔ARM Cortex-A9

NX бит помогает защитить компьютер от вирусных атак.

биты, передающиеся за то же время

128 (Apple Cyclone)

NEON обеспечивает ускорение обработки мультимедийных данных, таких, как прослушивание MP3.

Имеет AES

✔Apple A8 (Apple Cyclone)

✖ARM Cortex-A9

AES используется для ускорения шифрования и дешифрования.

версия VFP

4 (Apple Cyclone)

Вектор плавающей точки (VFP) используется процессором, чтобы обеспечить повышенную производительность в таких областях, как цифровые изображения.

Geekbench 5 результат (одноядерный)

Неизвестно. Помогите нам, предложите стоимость. (Apple A8)

Неизвестно. Помогите нам, предложите стоимость. (ARM Cortex-A9)

(ARM Cortex-A9)

Geekbench 5 — это кросс-платформенный тест, который измеряет одноядерную производительность процессора. (Источник: Primate Labs, 2023)

Geekbench 5 результат (многоядерный)

Неизвестно. Помогите нам, предложите стоимость. (Apple A8)

Неизвестно. Помогите нам, предложите стоимость. (ARM Cortex-A9)

Geekbench 5 — это кросс-платформенный тест, который измеряет производительность многоядерного процессора. (Источник: Primate Labs,2023)

результат PassMark

Неизвестно. Помогите нам, предложите стоимость. (Apple A8)

Неизвестно. Помогите нам, предложите стоимость. (ARM Cortex-A9)

Этот тест измеряет производительность процессора при помощи многопоточности.

результат PassMark (одиночный)

Неизвестно. Помогите нам, предложите стоимость. (Apple A8)

Неизвестно. Помогите нам, предложите стоимость. (ARM Cortex-A9)

Этот тест измеряет производительность процессора при помощи потока выполнения.

результат PassMark (разогнан)

Неизвестно. Помогите нам, предложите стоимость. (Apple A8)

Неизвестно. Помогите нам, предложите стоимость. (ARM Cortex-A9)

Этот тест измеряет производительность процессора в то время как он разогнан.

флопс

0.12 TFLOPS (Imagination Technologies PowerVR GX6450)

Неизвестно. Помогите нам, предложите стоимость.

FLOPS — это измерение вычислительной мощности процессора GPU.

This page is currently only available in English.

Веб-сайт разработчика ARM содержит документацию, учебные пособия, ресурсы поддержки и многое другое.

В течение следующих нескольких месяцев мы добавим дополнительные ресурсы для разработчиков и документацию по всем продуктам и технологиям, которые предоставляет ARM.

Закрыть

Перейти к основному содержанию Перейти к навигации в нижнем колонтитуле

Извините, ваш браузер не поддерживается. Мы рекомендуем обновить ваш браузер. Мы сделали все возможное, чтобы вся документация и ресурсы были доступны в старых версиях Internet Explorer, но поддержка векторных изображений и макет могут быть не оптимальными. Техническая документация доступна в формате PDF для загрузки.

Похоже, в вашем браузере отключен JavaScript.

В вашем браузере должен быть включен JavaScript, чтобы использовать функциональные возможности этого веб-сайта.

Техническое справочное руководство Cortex-A8

Руководство программиста Cortex-A Series для Armv7-A

Средства разработки для Cortex-A

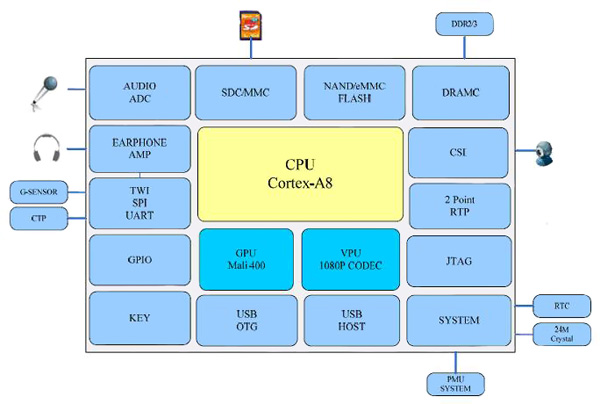

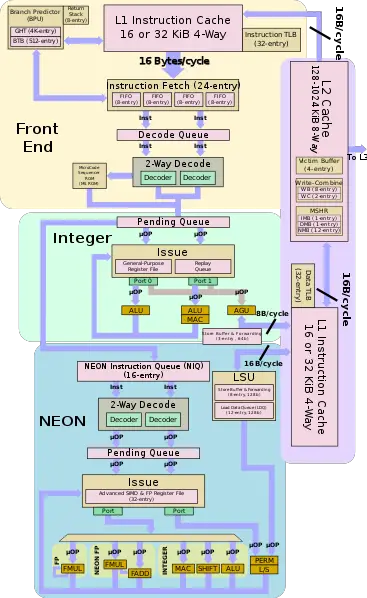

Процессор Cortex-A8 — это высокопроизводительный процессор приложений с низким энергопотреблением, обеспечивающий все возможности виртуальной памяти

Cortex-A8 был впервые представлен в 2005 году и стал первым процессором, поддерживающим архитектуру Armv7-A. С момента своего появления процессор Cortex-A8 был вытеснен процессорами Cortex-A15 и Cortex-A17, но он представляет собой поворотный момент в гонке за эффективными высокопроизводительными 32-разрядными вычислениями и по-прежнему широко используется в множество встроенных приложений.

С момента своего появления процессор Cortex-A8 был вытеснен процессорами Cortex-A15 и Cortex-A17, но он представляет собой поворотный момент в гонке за эффективными высокопроизводительными 32-разрядными вычислениями и по-прежнему широко используется в множество встроенных приложений.

| Архитектура | |

| Многоядерный | Только одножильный |

| Поддержка ISA |

|

| Блок управления памятью (MMU) | Блок управления памятью Armv7 (MMU) |

| Отладка и трассировка | CoreSight |

Сравните характеристики процессоров Cortex-A Armv7-A и Armv8-A:

Скачать сравнительную таблицу

Процессор Cortex-A8 первым использовал архитектуру Armv7-A.

Процессор имеет ряд особенностей, которые делают его идеальным для использования в высокопроизводительных конечных продуктах. Симметричный суперскалярный конвейер обеспечивает полную поддержку двух выпусков и высокочастотные конфигурации. Имеется усовершенствованный блок прогнозирования ветвлений с точностью более 95%, а встроенный кэш L2 обеспечивает оптимальную производительность в требовательных системах. Cortex-A8 поддерживает технологию Neon, что позволяет использовать преимущества ускоренной обработки мультимедиа и DSP.

Процессор Arm Cortex-A8 имеет возможность увеличения скорости от 600 МГц до более чем 1 ГГц, что соответствует требованиям к мобильным устройствам с оптимизированным энергопотреблением, которым требуется менее 300 мВт, и потребительским приложениям с оптимизированной производительностью.

Была ли эта страница полезной?

Да НетСпасибо! Мы ценим Ваш отзыв.

Введение

Микропроцессор ARM® Cortex™-A8 — это первый прикладной микропроцессор в новом семействе Cortex от ARM. Обладая высокой производительностью и энергоэффективностью, он предназначен для широкого спектра мобильных и потребительских приложений, включая мобильные телефоны, телевизионные приставки, игровые консоли и автомобильные навигационные/развлекательные системы.

Это первый процессор ARM, включающий все новые технологии, доступные в архитектуре ARMv7. Впервые представленные новые технологии включают NEON™ для обработки мультимедиа и сигналов и Jazelle® RCT для ускорения компиляторов реального времени. Другие недавно представленные технологии, которые теперь являются стандартными для архитектуры ARMv7, включают технологию TrustZone® для обеспечения безопасности, технологию Thumb®-2 для плотности кода и архитектуру с плавающей запятой VFPv3.

Обзор архитектуры Cortex

Объединяющей технологией процессоров Cortex является технология Thumb-2. Набор инструкций Thumb-2 объединяет 16- и 32-битные инструкции для повышения плотности кода и производительности. Исходный набор инструкций ARM состоит из 32-битных инструкций фиксированной длины, в то время как набор инструкций Thumb использует 16-битные инструкции. Поскольку не все операции отображались в исходном наборе инструкций Thumb, иногда требовалось несколько инструкций для имитации задачи одной 32-битной инструкции.

Технология Thumb-2 добавляет к Thumb около 130 дополнительных инструкций. Добавленная функциональность устраняет необходимость переключения между режимами ARM и Thumb для обслуживания прерываний и дает доступ к полному набору регистров процессора. Полученный код поддерживает традиционную плотность кода инструкций Thumb, работая с уровнями производительности 32-битного кода ARM. Целые приложения теперь могут быть написаны с использованием технологии Thumb-2, что исключает первоначальную архитектуру, необходимую для переключения режимов.

Целое приложение может быть написано с использованием компактных инструкций Thumb-2, тогда как в исходном режиме Thumb процессор должен был переключаться между режимами ARM и Thumb.

Впервые в процессоре ARM появилась технология обработки мультимедиа и сигналов NEON, ориентированная на аудио, видео и трехмерную графику. Это 64/128-битная гибридная SIMD-архитектура. Технология NEON имеет собственный регистровый файл и конвейер выполнения, которые отделены от основного целочисленного конвейера ARM. Он может обрабатывать как целые числа, так и значения с плавающей запятой одинарной точности, а также включает поддержку невыровненного доступа к данным и простую загрузку чередующихся данных, хранящихся в форме структуры. Используя технологию NEON для выполнения типичных мультимедийных функций, процессор Cortex-A8 может декодировать видео MPEG-4 VGA (включая dering, deblock фильтры и yuv2rgb) со скоростью 30 кадров/с на частоте 275 МГц и видео H.264 на частоте 350 МГц.

Также новой является технология Jazelle RCT, расширение архитектуры, которое сокращает объем памяти приложений байт-кода JIT до трети их исходного размера. Меньший размер кода приводит к повышению производительности и снижению энергопотребления.

Меньший размер кода приводит к повышению производительности и снижению энергопотребления.

Технология TrustZone включена в Cortex-A8 для обеспечения конфиденциальности данных и защиты DRM в потребительских товарах, таких как мобильные телефоны, персональные цифровые помощники и телевизионные приставки, работающие под управлением открытых операционных систем. Технология TrustZone, реализованная в ядре процессора, защищает периферийные устройства и память от атак безопасности. Защищенный монитор в ядре служит привратником, переключающим систему между безопасным и незащищенным состояниями. В безопасном состоянии процессор запускает «доверенный» код из безопасного блока кода для обработки чувствительных к безопасности задач, таких как аутентификация и манипулирование подписью.

Помимо повышения производительности обработки сигналов процессором, технология NEON позволяет использовать программные решения для приложений обработки данных. В результате получается гибкая платформа, которая может работать с новыми алгоритмами и новыми приложениями по мере их появления путем простой загрузки нового программного обеспечения или драйвера.

Технология VFPv3 является усовершенствованием технологии VFPv2. Новые функции включают удвоение количества регистров двойной точности до 32 и введение инструкций, которые выполняют преобразования между числами с фиксированной и плавающей запятой.

Изучение возможностей микроархитектуры Cortex-A8

Процессор Cortex-A8 — это самый совершенный процессор с низким энергопотреблением, когда-либо произведенный ARM. Для достижения высокого уровня производительности были добавлены новые функции микроархитектуры, которые традиционно не встречаются в архитектуре ARM, в том числе двойной целочисленный конвейер ARM с порядковым выпуском, интегрированный кэш L2 и глубокий 13-этапный конвейер.

Суперскалярный конвейер

Возможно, наиболее важной из этих новых функций является упорядоченный, статически запланированный целочисленный конвейер ARM с двойным выпуском. Предыдущие процессоры ARM имели только один целочисленный конвейер выполнения. Возможность одновременного выполнения двух инструкций по обработке данных значительно увеличивает максимально возможное количество инструкций, выполняемых за такт. Было решено оставить выпуск в порядке, чтобы свести к минимуму дополнительную мощность. Выпуск не по порядку и вывод из эксплуатации могут потребовать значительных объемов логики, потребляющей дополнительную мощность. Выбор по порядку также позволяет выдавать инструкции по принципу «выстрелил и забыл», тем самым удаляя критические пути из проекта и уменьшая потребность в индивидуальном дизайне в конвейере. Статическое планирование позволяет использовать обширную синхронизацию для снижения энергопотребления во время выполнения.

Было решено оставить выпуск в порядке, чтобы свести к минимуму дополнительную мощность. Выпуск не по порядку и вывод из эксплуатации могут потребовать значительных объемов логики, потребляющей дополнительную мощность. Выбор по порядку также позволяет выдавать инструкции по принципу «выстрелил и забыл», тем самым удаляя критические пути из проекта и уменьшая потребность в индивидуальном дизайне в конвейере. Статическое планирование позволяет использовать обширную синхронизацию для снижения энергопотребления во время выполнения.

Двойные конвейеры ALU (арифметико-логического устройства) (ALU 0 и ALU 1) симметричны, и оба могут обрабатывать большинство арифметических инструкций. Канал ALU 0 всегда несет более старую из пары выпущенных инструкций. Процессор Cortex-A8 также имеет конвейеры умножения и загрузки-сохранения, но они не несут дополнительных инструкций для двух конвейеров ALU. Их можно рассматривать как «зависимые» конвейеры. Их использование требует одновременного использования одного из конвейеров АЛУ. Конвейер умножителя может быть связан только с инструкциями, которые находятся в конвейере ALU 0, тогда как конвейер загрузки-сохранения может быть связан с инструкциями в любом из ALU.

Конвейер умножителя может быть связан только с инструкциями, которые находятся в конвейере ALU 0, тогда как конвейер загрузки-сохранения может быть связан с инструкциями в любом из ALU.

Branch Prediction

13-этапный конвейер был выбран для обеспечения значительно более высоких рабочих частот, чем драгоценные поколения микроархитектур ARM. Обратите внимание, что этап F0 не учитывается, потому что это только генерация адреса. Чтобы свести к минимуму штрафы за ветвления, обычно связанные с более глубоким конвейером, процессор Cortex-A8 реализует двухуровневый предсказатель ветвлений глобальной истории. Он состоит из двух разных структур: целевого буфера перехода (BTB) и буфера глобальной истории (GHB), доступ к которым осуществляется параллельно с выборкой инструкций.

BTB указывает, будет ли текущий адрес выборки возвращать инструкцию ветвления и целевой адрес ветвления. Он содержит 512 записей. При попадании в BTB прогнозируется ветвь и осуществляется доступ к GHB. GHB состоит из 4096 2-битных счетчиков насыщения, которые кодируют информацию о силе и направлении ветвей. GHB индексируется 10-битной историей направления последних десяти ответвлений и 4 битами ПК.

GHB состоит из 4096 2-битных счетчиков насыщения, которые кодируют информацию о силе и направлении ветвей. GHB индексируется 10-битной историей направления последних десяти ответвлений и 4 битами ПК.

В дополнение к динамическому предсказателю ветвлений стек возврата используется для предсказания адресов возврата подпрограммы. Стек возврата имеет восемь 32-битных записей, в которых хранится значение регистра связи в r14 (регистр 14) и состояние ARM или Thumb вызывающей функции. Когда предсказывается выполнение инструкции возвращаемого типа, стек возврата предоставляет последний отправленный адрес и состояние.

Кэш-память уровня 1

Процессор Cortex-A8 имеет штраф за использование нагрузки за один цикл для быстрого доступа к кэш-памяти уровня 1. Кэш данных и инструкций можно настроить на 16 КБ или 32 КБ. Каждый из них имеет 4-канальную ассоциативность и использует схему прогнозирования пути хеш-буфера виртуального адреса (HVAB) для улучшения синхронизации и снижения энергопотребления. Кэши имеют физическую адресацию (виртуальный индекс, физический тег) и имеют аппаратную поддержку, позволяющую избежать псевдонимов записей. Контроль четности поддерживается одним битом четности на байт.

Кэши имеют физическую адресацию (виртуальный индекс, физический тег) и имеют аппаратную поддержку, позволяющую избежать псевдонимов записей. Контроль четности поддерживается одним битом четности на байт.

Политика замены кэша данных — обратная запись без выделения памяти для записи. Также включен буфер хранения для слияния данных перед записью в основную память.

HVAB — это новый подход к снижению мощности, необходимой для доступа к кэшам. Он использует схему прогнозирования, чтобы определить, какой способ ОЗУ включить перед доступом.

Кэш-память 2-го уровня

Процессор Cortex-A8 включает встроенную кэш-память 2-го уровня. Это дает кешу уровня 2 выделенный интерфейс с малой задержкой и высокой пропускной способностью для кеша уровня 1. Это минимизирует задержку заполнения строк кэша уровня 1 и не конфликтует с трафиком на основной системной шине. Его можно настроить в размерах от 64k до 2M.

Кэш-память 2-го уровня имеет физическую адресацию и 8-канальную ассоциативность. Это унифицированный кэш данных и инструкций, который поддерживает дополнительные ECC и Parity. Политики обратной записи, сквозной записи и записи-распределения соблюдаются в соответствии с настройками таблицы страниц. Используется псевдослучайная политика распределения. Содержимое кэша данных уровня 1 является эксклюзивным для кэша уровня 2, тогда как содержимое кэша инструкций уровня 1 является подмножеством кэша уровня 2. Доступ к ОЗУ тегов и данных кэш-памяти уровня 2 осуществляется последовательно для экономии энергии.

Это унифицированный кэш данных и инструкций, который поддерживает дополнительные ECC и Parity. Политики обратной записи, сквозной записи и записи-распределения соблюдаются в соответствии с настройками таблицы страниц. Используется псевдослучайная политика распределения. Содержимое кэша данных уровня 1 является эксклюзивным для кэша уровня 2, тогда как содержимое кэша инструкций уровня 1 является подмножеством кэша уровня 2. Доступ к ОЗУ тегов и данных кэш-памяти уровня 2 осуществляется последовательно для экономии энергии.

Медиа-движок NEON

Конвейер медиа-процессора NEON процессора Cortex-A8 начинается в конце основного целочисленного конвейера. В результате все исключения и неправильные предсказания переходов разрешаются до того, как до них дойдут инструкции. Что еще более важно, существует нулевой штраф за использование загрузки для данных в кэше уровня 1. Целочисленный блок ARM генерирует адреса для загрузки и сохранения NEON по мере их прохождения по конвейеру, что позволяет извлекать данные из кэша уровня 1 до того, как они потребуются операцией обработки данных NEON. Глубокая буферизация инструкций и данных загрузки между движком NEON, целочисленным блоком ARM и системой памяти позволяет скрыть задержку доступа уровня 2 для потоковых данных. Буфер хранилища не позволяет хранилищам NEON блокировать конвейер и обнаруживает конфликты адресов с доступом к целочисленным единицам ARM и загрузками NEON.

Глубокая буферизация инструкций и данных загрузки между движком NEON, целочисленным блоком ARM и системой памяти позволяет скрыть задержку доступа уровня 2 для потоковых данных. Буфер хранилища не позволяет хранилищам NEON блокировать конвейер и обнаруживает конфликты адресов с доступом к целочисленным единицам ARM и загрузками NEON.

Блок NEON отделен от основного целочисленного конвейера ARM очередью инструкций NEON (NIQ). Блок выполнения инструкций ARM может выдавать до двух действительных инструкций блоку NEON за каждый такт. NEON имеет 128-битные пути загрузки и хранения к кешу уровня 1 и уровня 2 и поддерживает потоковую передачу из обоих.

Медиа-движок NEON имеет собственный 10-этапный конвейер, который начинается в конце целочисленного конвейера ARM. Поскольку все неправильные предсказания и исключения были разрешены в целочисленной единице ARM, после того, как инструкция была выдана медиа-движку NEON, она должна быть завершена, поскольку она не может генерировать исключения. NEON имеет три целочисленных конвейера SIMD, конвейер загрузки-хранения/перестановки, два конвейера SIMD одинарной точности с плавающей запятой и неконвейерный блок векторных вычислений с плавающей запятой (VFPLite).

NEON имеет три целочисленных конвейера SIMD, конвейер загрузки-хранения/перестановки, два конвейера SIMD одинарной точности с плавающей запятой и неконвейерный блок векторных вычислений с плавающей запятой (VFPLite).

Инструкции NEON выдаются и удаляются по порядку. Инструкция обработки данных представляет собой целочисленную инструкцию NEON или инструкцию NEON с плавающей запятой. Блок Cortex-A8 NEON не выполняет параллельную выдачу двух инструкций по обработке данных, чтобы избежать накладных расходов на область из-за дублирования функциональных блоков обработки данных, а также избежать критических по времени путей и сложностей, связанных с мультиплексированием портов регистров чтения и записи.

Путь целочисленных данных NEON состоит из трех конвейеров: целочисленного конвейера умножения/накопления (MAC), целочисленного конвейера сдвига и целочисленного конвейера ALU. Конвейер загрузки-хранения/перестановки отвечает за всю загрузку/сохранение NEON, передачу данных в/из целочисленного блока и операции перестановки данных, такие как чередование и обратное чередование. Путь данных NEON с плавающей запятой (NFP) имеет два основных конвейера: конвейер умножения и конвейер добавления. Отдельный модуль VFPLite представляет собой неконвейерную реализацию ARM 9.0003

Путь данных NEON с плавающей запятой (NFP) имеет два основных конвейера: конвейер умножения и конвейер добавления. Отдельный модуль VFPLite представляет собой неконвейерную реализацию ARM 9.0003

VFPv3 Floating Point Спецификация предназначена для средней производительности, совместимой с поддержкой IEEE 754 с плавающей запятой. VFPLite используется для обеспечения обратной совместимости с существующим кодом с плавающей запятой ARM и для обеспечения арифметики с одинарной и двойной точностью, совместимой со стандартом IEEE 754. «Lite» относится к площади и производительности, а не к функциональности.

Реализация

Из-за высоких показателей производительности, мощности и площади (PPA) процессора Cortex-A8 были разработаны новые потоки реализации для достижения поставленных целей, не прибегая к полностью настраиваемой реализации. Результирующие потоки позволяют точно настроить дизайн для желаемого приложения. Результатом является, по сути, поток на основе ячеек, но в его основе лежат полунастраиваемые методы, которые использовались там, где это было необходимо для обеспечения производительности.

Процессор Cortex-A8 использует комбинацию синтезированных, структурированных и пользовательских схем. Проект был разделен на семь функциональных блоков, а затем подразделен на блоки, для каждого из которых был выбран соответствующий метод реализации. Поскольку весь дизайн является синтезируемым, блоки, которые могут легко достичь своих целей PPA, могут придерживаться стандартного потока синтеза.

Структурированный поток используется для блоков, которые содержат логику, которая может использовать преимущества управляемого подхода к размещению и маршрутизации для достижения целей по времени или площади. Этот подход представляет собой полунастраиваемый поток, который вручную отображает блок в список соединений уровня шлюза и указывает относительное размещение для всех ячеек в блоке. Относительное размещение определяет не точное расположение ячеек, а то, как каждая ячейка размещается по отношению к другим ячейкам в блоке.

Структурированный подход обычно используется для блоков данных, имеющих регулярную структуру. Логическая реализация и технологическое отображение блока выполняются вручную, чтобы поддерживать обычную структуру шины блока, ориентированную на данные, вместо создания случайной структуры вентиля посредством синтеза. Логические элементы блока размещаются в соответствии с потоком данных через блок. Этот подход предлагает больший контроль над проектом, чем подход автоматизированного синтеза, и приводит к более предсказуемому времени закрытия. Также можно получить лучшую производительность и площадь на сложных, высокопроизводительных конструкциях, чем традиционные методы. Полученные списки соединений можно интерпретировать с помощью традиционных методов мозаичного построения с использованием ARM Artisan® Advantage-CE™ или совместимой библиотеки.

Логическая реализация и технологическое отображение блока выполняются вручную, чтобы поддерживать обычную структуру шины блока, ориентированную на данные, вместо создания случайной структуры вентиля посредством синтеза. Логические элементы блока размещаются в соответствии с потоком данных через блок. Этот подход предлагает больший контроль над проектом, чем подход автоматизированного синтеза, и приводит к более предсказуемому времени закрытия. Также можно получить лучшую производительность и площадь на сложных, высокопроизводительных конструкциях, чем традиционные методы. Полученные списки соединений можно интерпретировать с помощью традиционных методов мозаичного построения с использованием ARM Artisan® Advantage-CE™ или совместимой библиотеки.

Библиотека Artisan Advantage-CE содержит более тысячи ячеек. Помимо стандартных ячеек, в которых используются типичные библиотеки синтеза, многие тактические ячейки включены в большей степени в соответствии с пользовательскими методами реализации. Они используются автоматически в структурированном потоке. Библиотека специально разработана для удовлетворения требований высокой плотности маршрутизации высокопроизводительных процессоров с упором как на высокую скорость работы, так и на низкую статическую и динамическую мощность. Уменьшение утечек достигается за счет ячеек MT-CMOS со стробированием питания и удерживающих триггеров для поддержки режимов сна и ожидания. ARM работала с поставщиками инструментов, чтобы обеспечить поддержку этого важного нового потока.

Они используются автоматически в структурированном потоке. Библиотека специально разработана для удовлетворения требований высокой плотности маршрутизации высокопроизводительных процессоров с упором как на высокую скорость работы, так и на низкую статическую и динамическую мощность. Уменьшение утечек достигается за счет ячеек MT-CMOS со стробированием питания и удерживающих триггеров для поддержки режимов сна и ожидания. ARM работала с поставщиками инструментов, чтобы обеспечить поддержку этого важного нового потока.

Наконец, несколько наиболее критичных по времени и площади блоков дизайна зарезервированы для полностью настраиваемых методов. Сюда входят массивы памяти, регистровые файлы и табло. Эти блоки содержат смесь статической и динамической логики. Самосинхронные цепи не используются.

Заключение

Процессор Cortex-A8 — самый быстрый и энергоэффективный микропроцессор, когда-либо разработанный ARM. Благодаря способности декодировать видео VGA H.264 на частоте менее 350 МГц он обеспечивает мощность обработки мультимедиа, необходимую для беспроводных и потребительских продуктов следующего поколения, при этом потребляя менее 300 мВт в 65-нм технологиях. Его новая технология NEON обеспечивает платформу для гибких программных решений для обработки мультимедиа. Инструкции Thumb-2 обеспечивают плотность кода при сохранении производительности стандартного кода ARM; Технология Jazelle RCT делает то же самое для компиляторов реального времени. Технология TrustZone обеспечивает безопасность конфиденциальных данных и DRM.

Его новая технология NEON обеспечивает платформу для гибких программных решений для обработки мультимедиа. Инструкции Thumb-2 обеспечивают плотность кода при сохранении производительности стандартного кода ARM; Технология Jazelle RCT делает то же самое для компиляторов реального времени. Технология TrustZone обеспечивает безопасность конфиденциальных данных и DRM.

Многие важные новые функции микроархитектуры впервые появляются в процессоре Cortex-A8. К ним относятся двойная проблема, упорядоченный суперскалярный конвейер, интегрированный кэш-память уровня 2 и значительно более глубокий конвейер, чем у ценных процессоров ARM. Для достижения своих высоких целей производительности при сохранении традиционного бюджета ARM на малую мощность были разработаны новые потоки, которые приближаются к эффективности пользовательских методов, сохраняя при этом гибкость автоматизированного потока. Процессор Cortex-A8 — это квантовый скачок в гибкой высокопроизводительной обработке с низким энергопотреблением.

Сноска:

Новое соглашение ARM по именованию процессоров

С анонсом процессора Cortex™-M3 ARM ввела новую схему именования для своих процессоров. Раньше процессоры назывались по базовому процессорному ядру, например ARM7™, ARM9™ и ARM11™, а цифры добавлялись для обозначения характеристик этого варианта процессора. Таким образом, ARM926EJ-S™ был основан на микроархитектуре ARM9, а цифры были добавлены для обозначения системы памяти, поддержки Java и арифметических расширений.

Новая схема именования ARM основана на поколении архитектуры процессора, а не на последовательности поступления самого процессора. (В ARM под архитектурой понимается набор инструкций/функций, общий для группы процессоров.) Ядра, относящиеся к последнему поколению архитектуры ARM, ARMv7, будут называться процессорами Cortex. Следующее поколение процессоров получит еще одно новое имя. Это было сделано для более четкого понимания относительной производительности и целевого применения нового процессора из его названия.