| Название | Тип | Описание |

|---|---|---|

| Core-0 | Аппаратная платформа | «Core-0» организует в FPGA микросхеме микропроцессорную систему на базе MicroBlaze с поддержкой работы с шиной PCI Express в режиме «Endpoint».

В состав «Core-0» входят две инфраструктуры IP-ядер:

|

| Core-1 | Аппаратная платформа | «Core-1» организует в FPGA микросхеме микропроцессорную систему на базе MicroBlaze с поддержкой работы с шиной PCI Express в режиме «Endpoint» и субмодулем FMC SFM-4A250.

В состав «Core-1» входят три инфраструктуры IP-ядер:

|

| Core-2 | Аппаратная платформа | «Core-2» организует в FPGA микросхеме микропроцессорную систему на базе MicroBlaze с поддержкой работы с шиной PCI Express в режиме «Endpoint» и субмодулем FMC SFM-1A5000.

В состав «Core-2» входят три инфраструктуры IP-ядер:

|

| Core-3 | Аппаратная платформа | «Core-3» организует в FPGA микросхеме микропроцессорную систему на базе MicroBlaze с поддержкой работы с шиной PCI Express в режиме «Endpoint» и субмодулем FMC SFM-2A1000-2D1000.

В состав «Core-3» входят три инфраструктуры IP-ядер:

|

| Core-4 | Аппаратная платформа | «Core-4» организует в FPGA микросхеме микропроцессорную систему на базе MicroBlaze с поддержкой работы с шиной PCI Express в режиме «Endpoint» и FMC модулем SFM-4D1000.

В состав «Core-4» входят три инфраструктуры IP-ядер:

|

| Микропроцессорная система на MicroBlaze | Инфраструктура IP-ядер | Набор IP-ядер, предназначенных для построения в FPGA Xilinx микропроцессорной системы на основе микропроцессорного IP-ядра MicroBlaze. |

| Поддержка PCI Express | Инфраструктура IP-ядер | Набор IP-ядер, позволяющий реализовать в FPGA Xilinx поддержку обмена потоками данных между устройствами, подключенными к AXI шине и шиной PCI Express. |

| Поддержка субмодуля SFM-1A5000 | Инфраструктура IP-ядер | Набор IP-ядер для организации инфраструктуры обмена потоковыми данными между FPGA Xilinx и субмодулем аналого-цифровой обработки SFM-1A5000 с использованием шины AXI4-Stream. |

| Поддержка субмодуля SFM-2A1000-2D1000 | Инфраструктура IP-ядер | Набор IP-ядер для организации инфраструктуры обмена потоковыми данными между FPGA Xilinx и субмодулем аналого-цифровой и цифро-аналоговой обработки SFM-2A1000-2D1000 с использованием шины AXI4-Stream. |

| Поддержка субмодуля SFM-4A250 | Инфраструктура IP-ядер | Набор IP-ядер для организации инфраструктуры обмена потоковыми данными между FPGA Xilinx и субмодулем аналого-цифровой обработки SFM-4A250 с использованием шины AXI4-Stream. |

| Поддержка субмодуля SFM-4D1000 | Инфраструктура IP-ядер | Набор IP-ядер для организации инфраструктуры обмена потоковыми данными между FPGA Xilinx и субмодулем цифро-аналоговой обработки SFM-4D1000 с использованием шины AXI4-Stream.

|

| Подсистема субмодуля SFM-4A250 | Инфраструктура IP-ядер | Предназначена для реализации контроллера субмодуля SFM-4A250, обеспечивающий начальную инициализацию, калибровку АЦП и интерфейс управления субмодулем, а также формирование двух потоков данных от АЦП по шинам AXI-Stream. |

| ADC контроллер | IP-ядро | Предоставляет возможность организации интерфейса взаимодействия FPGA c микросхемой аналого-цифрового преобразователя, установленной на субмодуле FMC. |

| DAC контроллер | IP-ядро | Предоставляет возможность организации интерфейса взаимодействия FPGA c микросхемой цифро-аналогового преобразователя, установленной на субмодуле FMC. |

| DM контроллер | IP-ядро | Предоставляет возможность контроля и управления работой IP-ядра AXI DataMover фирмы Xilinx. Совместно с AXI DataMover обеспечивает трансляцию потоковых данных.

|

| FMC контроллер | IP-ядро | Предоставляет возможность управления набором микросхем, расположенных на ряде субмодулей FMC и подключенных к отдельной микросхеме управления на базе CPLD. |

| Частотомер | IP-ядро | Предоставляет возможность измерения значений частот периодически повторяющихся сигналов, поступающих на соответствующие входы IP-ядра. |

| Конвертер потоков AXI и PCIe | IP-ядро | Предоставляет возможность конвертации потоков данных, транслируемых между интерфейсами AXI4 и PCIe. |

| Конвертер потоков AXI и Serial RapidIO | IP-ядро | Предоставляет возможность конвертации потоков данных, транслируемых между интерфейсами AXI4 и Serial RapidIO. |

| Сервисные регистры | IP-ядро | Предоставляет набор сервисных функций в ориентированных на использование технологии PCI Express системных решениях. |

| Ten Gigabit AXI-Stream controller | IP-ядро | Предназначено для организации межкристального взаимодействия с канальной скоростью 10 Гбит/с по протоколу AXI-Stream в пакетном режиме. |

| ADC 2A250 controller | IP-ядро | Предназначено для реализации контроллера АЦП ADS62P4X, позволяющего калибровать АЦП и формировать два потока данных от АЦП по шинам AXI-Stream |

| FreeRTOS FPGA Demo | Приложение для MicroBlaze | Демонстрационный проект приложения на базе ОС FreeRTOS, исполняемого на микропроцессорном ядре MicroBlaze. |

| Загрузчик MBL | Приложение для MicroBlaze | Демонстрационный проект приложения для загрузки из энергонезависимой флэш-памяти в DDR SDRAM исполняемого двоичного кода, предназначенного для исполнения микропроцессорной системой на базе MicroBlaze.

|

Для

взаимодействия с памятью на чипе со

стороны FPGA в соответствии со структурным

подходом к проектированию разработаны

три отдельных подмодуля: подмодуль для

выгрузки служебной информации

(eth_service),

подмодуль для выгрузки и передачи

входных данных в модули цепочки первичной

обработки (eth_read),

подмодуль для загрузки выходных данных

цепочки первичной обработки в память

на чипе (eth_write). Разработка модулей велась с помощью

ЯПА Verilog.

Выбор

именно этого языка для описания модулей

обусловлен прошлым знакомством с ним

в рамках учебного плана, а также более

простым, чем у альтернатив, написанием

testbench.

Оформление производилось в соответствии

с правилами документации проектов для

ПЛИС

[20]

и требованиями по единой системе

программной документации. [21,

22]

Разработка модулей велась с помощью

ЯПА Verilog.

Выбор

именно этого языка для описания модулей

обусловлен прошлым знакомством с ним

в рамках учебного плана, а также более

простым, чем у альтернатив, написанием

testbench.

Оформление производилось в соответствии

с правилами документации проектов для

ПЛИС

[20]

и требованиями по единой системе

программной документации. [21,

22]

Схематические обозначения подмодулей представлены на рисунке 2.5.

Рисунок 2.5 – Подмодули взаимодействия с памятью на чипе

Каждый модуль представляет из себя конечный автомат, выполняющий операции с блоком памяти на чипе. Рассмотрим каждый подмодуль подробнее.

Листинг 2.1 содержит заголовок модуля eth_service.

Листинг 2.1 – Объявление и порты подмодуля eth_service

Данный

подмодуль производит выгрузку служебной

информации из служебного блока памяти

на чипе и запись ее в регистры в FPGA-части

для дальнейшего использования, до начала

работы устанавливает выходной сигнал finished,

начинает работу по нижнему уровню

входного сигнала reset,

в конце работы сбрасывает сигнал finished. Взаимодействие с блоком памяти на чипе

производится через двунаправленные

порты service_address (шина

адреса блока памяти), service_readdata (шина

считывания данных с блока памяти), service_write (флаг

записи данных в блок памяти, требует

отдельного выставления после каждой

смены адреса). Подмодуль тактируется

входным сигналом clock и

имеет выходами считанные значения

служебных признаков (number_of_channels,

first_block_id, last_block_id, data_length).

Взаимодействие с блоком памяти на чипе

производится через двунаправленные

порты service_address (шина

адреса блока памяти), service_readdata (шина

считывания данных с блока памяти), service_write (флаг

записи данных в блок памяти, требует

отдельного выставления после каждой

смены адреса). Подмодуль тактируется

входным сигналом clock и

имеет выходами считанные значения

служебных признаков (number_of_channels,

first_block_id, last_block_id, data_length).

Заголовок модуля eth_read представлен в листинге 2.2.

Листинг 2.2 – Объявление и порты подмодуля eth_read

Данный подмодуль производит выгрузку данных из одного из блоков входных данных. Как и подмодуль eth_service, eth_read имеет три двунаправленных порта для взаимодействия с блоком памяти – input_address

Подмодуль начинает

работу по нижнему уровню входного

сигнала reset и

до начала работы устанавливает выходные

сигналы input_finished и done. Первый

сигнал модуль сбрасывает по окончании

считывания блока данных, начальный

адрес begin_addr и

размер addr_span которого

задаются соответствующими входами,

второй сигнал модуль импульсно сбрасывает

после каждого считанного значения, считываемое

значение подается на выходную шину read_data_output, ширина

которой задается параметром read_data_output_length. Подмодуль тактируется сигналом clock.

Подмодуль начинает

работу по нижнему уровню входного

сигнала reset и

до начала работы устанавливает выходные

сигналы input_finished и done. Первый

сигнал модуль сбрасывает по окончании

считывания блока данных, начальный

адрес begin_addr и

размер addr_span которого

задаются соответствующими входами,

второй сигнал модуль импульсно сбрасывает

после каждого считанного значения, считываемое

значение подается на выходную шину read_data_output, ширина

которой задается параметром read_data_output_length. Подмодуль тактируется сигналом clock.В листинге 2.3 представлен заголовок модуля eth_write.

Листинг 2.3 – Объявление и порты модуля eth_write

Данный

подмодуль производит загрузку значений

на выходе тестируемого модуля (тестируемой

цепочки?) в блок памяти на чипе для

выходных данных. Как и предыдущие два

подмодуля, eth_write взаимодействует

с блоком памяти на чипе через три

двунаправленных порта: шину адреса output_address, шину

записи данных в блок output_writedata и флаг записи данных output_write, который

выставляется для определенного адреса

после произведенной операции записи. Область записи данных в блок памяти

задается входами begin_addr(начальный

адрес) и addr_span(количество

данных для записи). Подмодуль до начала

работы выставляет выходной сигнал done, начинает работу по нижнему уровню

сигнала reset, по

окончании работы сбрасывает сигнал done. Данные

для записи в память подаются на шину write_data_input, ширина

которой определяется параметром write_data_input_length. Подмодуль

тактируется сигналом clock.

Область записи данных в блок памяти

задается входами begin_addr(начальный

адрес) и addr_span(количество

данных для записи). Подмодуль до начала

работы выставляет выходной сигнал done, начинает работу по нижнему уровню

сигнала reset, по

окончании работы сбрасывает сигнал done. Данные

для записи в память подаются на шину write_data_input, ширина

которой определяется параметром write_data_input_length. Подмодуль

тактируется сигналом clock.

Для работы с несколькими блоками данных, как входных, так и выходных, можно объявлять несколько подмодулей eth_read или eth_write. В начале тестирования первым выполняется модуль eth_service, после окончания его работы в зависимости от условий тестирования запускаются модули eth_read и eth_write. Тестирование считается завершенным, когда завершает работу модуль eth_write.

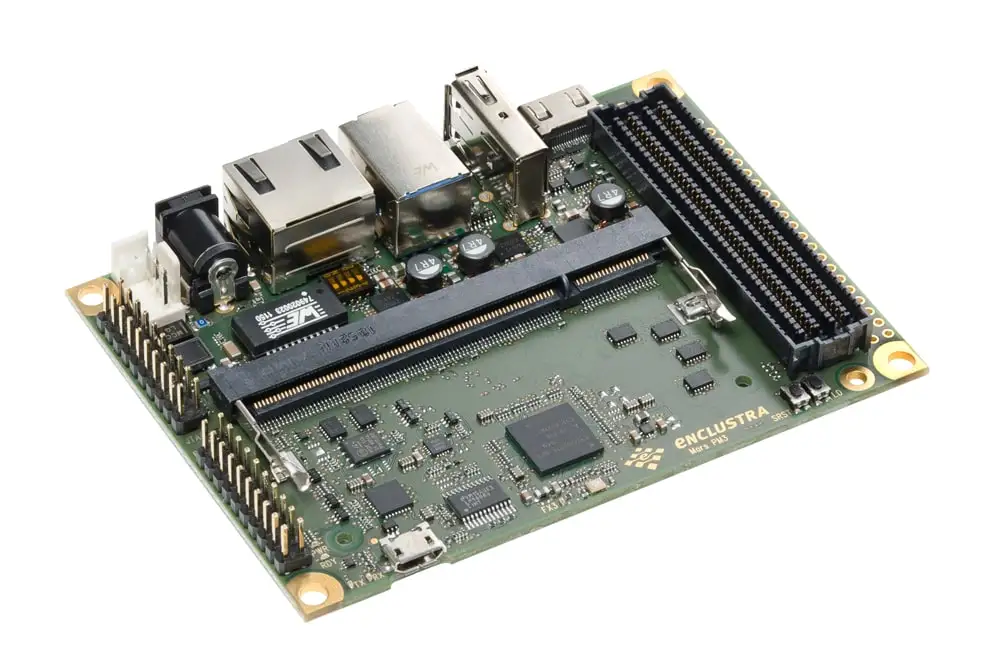

Платы FPGA Acromag для встраиваемых приложений с использованием модулей FPGA на базе XMC, PMC и mPCIe оснащены настраиваемой пользователем Xilinx ® FPGA. Эти модули позволяют разрабатывать и хранить в FPGA собственные наборы инструкций для различных адаптивных вычислительных приложений.

Эти модули позволяют разрабатывать и хранить в FPGA собственные наборы инструкций для различных адаптивных вычислительных приложений.

Выберите одну из нескольких моделей, содержащих до 410 тыс. логических ячеек, оптимизированных для логики, DSP или PowerPC. Высокоскоростная память и интерфейсы быстрой шины позволяют быстро перемещать данные.

Модули FPGA на основе mPCIe

Zync® UltraScale+ MPSoC | Artix-7

Модули XMC FPGA

Artix-7 | Кинтекс-7 | Spartan-6

Благодаря мощностям Zynq® UltraScale+™ MPSoC

для обработки ввода-вывода и программируемой логики.

Нажмите здесь, чтобы узнать больше

Чтобы помочь вам в разработке пользовательских программ, Acromag предлагает комплект для проектирования. Этот комплект содержит утилиты, помогающие загружать VHDL в FPGA и устанавливать передачи DMA между FPGA и ЦП. Наборы включают скомпилированный файл FPGA и пример кода VHDL для интерфейса локальной шины, прерываний чтения/записи и изменения состояния шины. Простое руководство по созданию ПЛИС

Наборы включают скомпилированный файл FPGA и пример кода VHDL для интерфейса локальной шины, прерываний чтения/записи и изменения состояния шины. Простое руководство по созданию ПЛИС

Компания Acromag предлагает набор для быстрого старта, который упрощает и ускоряет разработку. Узнайте больше об этом комплекте для разработки FPGA.

Эти реконфигурируемые модули FPGA основаны на электромеханических характеристиках мини-карты PCI Express и имеют длину 70 мм с дополнительным 100-контактным разъемом ввода-вывода. АкроПаку 19 летНа 0,05 мм длиннее полноразмерной карты mini PCIe (50,95 мм). Он имеет такую же ширину платы mPCIe, равную 30 мм, и использует ту же самую стандартную плату mPCIe, удерживающую зазор и завинчивающиеся области.

Модуль APZU+ представляет собой базовый модуль Xilinx Zynq с матрицей FPGA, доступной для приложений параллельных вычислений. Ключевая информация, полученная в результате параллельной обработки, затем может быть передана в систему обработки ARM для дальнейшей обработки и обработки.

APZU+ использует современную технологию поверхностного монтажа (SMT) для достижения своей широкой функциональности и является идеальным выбором для широкого спектра промышленных приложений ввода-вывода, которым требуется высокоплотный, высоконадежный и высокопроизводительный интерфейс на низкая стоимость.

APA7-500: модуль FPGA AcroPack, цифровой интерфейс с большим количеством каналов: опции интерфейса RS485, LVDS и TTL.

Эти модули обеспечивают настраиваемый пользователем мост на базе FPGA между хост-процессором и настраиваемым цифровым интерфейсом через PCI Express. Четыре модели поддерживают различные стандарты цифрового ввода-вывода. Модули оснащены программируемой пользователем FPGA серии Xilinx Artix-7. Реконфигурация ПЛИС возможна путем прямой загрузки во флэш-память конфигурации по шине PCIe. Встроенная флэш-память, загруженная данными конфигурации, позволяет автоматически конфигурировать ПЛИС при включении питания.

Встроенная флэш-память, загруженная данными конфигурации, позволяет автоматически конфигурировать ПЛИС при включении питания.

Эти модули включают однополосный интерфейс PCIe (PCI Express) с одним каналом прямого доступа к памяти для передачи данных между шиной PCIe и блочной памятью FPGA.

Плата оснащена 32 Мб памяти Quad Serial Flash. Флэш-память обеспечивает хранилище для конфигурации FPGA.

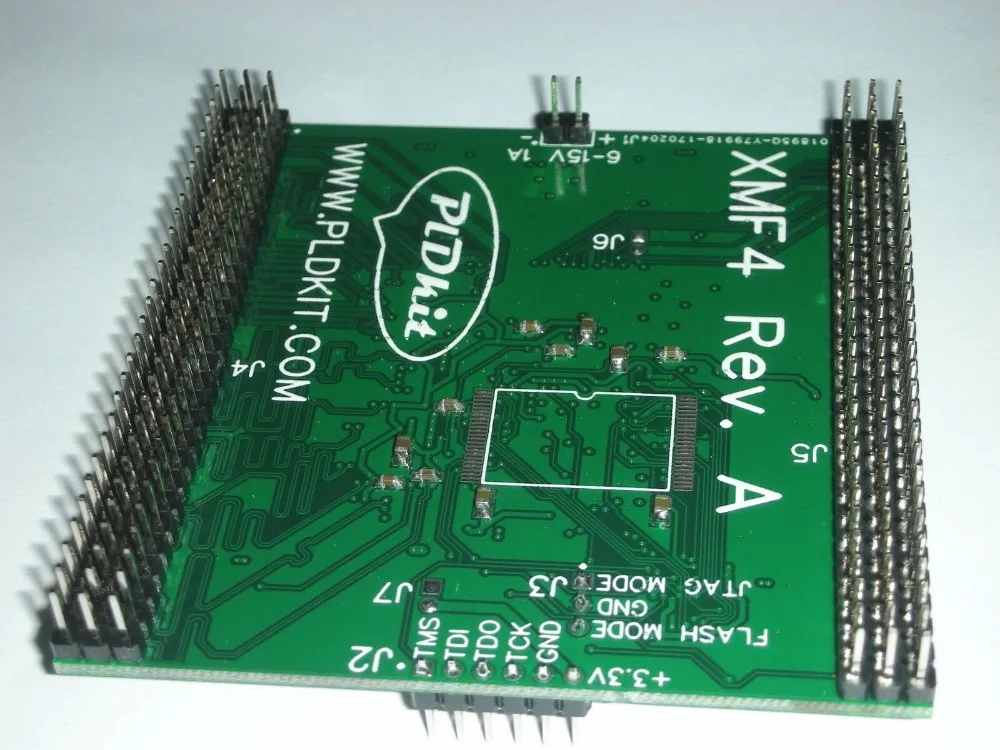

Reconfigurable Xilinx FPGA — В системе конфигурация FPGA реализована через стандартный интерфейс JTAG или шину PCIe. Это обеспечивает средства для реализации пользовательских дизайнов.

XMC-7A: модуль XMC FPGA с интерфейсом PCIe, вставными мезонинными модулями расширения ввода-вывода, передним или задним вводом-выводом.

XMC-7ACC: модуль XMC FPGA с интерфейсом PCIe, кондуктивное охлаждение.

XMC-7AWP: модуль XMC FPGA с интерфейсом PCIe, флэш-память с защитой от записи.

Эти реконфигурируемые модули FPGA включают следующие интерфейсы: Четыре или восемь высокоскоростных последовательных линий выделяются для разъема XMC P15. Эти линии можно использовать для PCIe (PCI Express), Serial RapidIO или 10 Gigabit Ethernet. Пример проекта будет поддерживать реализацию PCIe Gen 1 с четырьмя или восемью линиями с одним каналом DMA для передачи данных между шиной PCIe и встроенной памятью DDR3.

Восемь или четыре высокоскоростных последовательных канала также выделены для разъема XMC P16. Эти последовательные линии можно использовать для Serial RapidIO, PCIe, Gigabit Ethernet, XAUI или Xilinx Aurora. Пример проекта будет поддерживать двойные интерфейсы Aurora для использования этих дорожек. Два глобальных тактовых сигнала и 34 выбранных сигнала ввода-вывода также будут доступны на разъеме P16. Выбор сигналов ввода-вывода — это контакты ввода-вывода 2,5 В, которые можно выбрать из стандартов несимметричного ввода-вывода (LVCMOS, HSTL и SSTL) и стандартов дифференциального ввода-вывода (LVDS, HT, LVPECL, BLVDS, дифференциальных HSTL и SSTL). ).

).

Разъем ввода-вывода P4 на задней панели обеспечивает две пары глобальных дифференциальных часов и 30 пар сигналов LVDS.

Плата имеет 128 Мб x 64-бит DDR3 SDRAM и 32 Мб x 16-бит параллельную Flash. Параллельная флэш-память обеспечивает хранение как данных конфигурации FPGA, так и памяти программ ЦП MicroBlaze.

XMC-7K: модуль XMC FPGA с интерфейсом PCIe, подключаемые мезонинные модули расширения ввода-вывода.

XMC-7K CC: модуль XMC FPGA с интерфейсом PCIe, кондуктивное охлаждение.

XMC-7K F: Модуль XMC FPGA с интерфейсом PCIe и SFP+/Aurora, два порта SFP+.

XMC-7KWP: модуль XMC FPGA с интерфейсом PCIe, флэш-память с защитой от записи.

Эти модули представляют собой модули XMC, в основе конструкции которых лежит перепрограммируемая FPGA Xilinx 7-й серии. Реконфигурация ПЛИС возможна путем прямой загрузки во флэш-память конфигурации по шине PCIe. Встроенная флэш-память, загруженная данными конфигурации, позволяет автоматически конфигурировать ПЛИС при включении питания.

Реконфигурация ПЛИС возможна путем прямой загрузки во флэш-память конфигурации по шине PCIe. Встроенная флэш-память, загруженная данными конфигурации, позволяет автоматически конфигурировать ПЛИС при включении питания.

Эти модули включают следующие интерфейсы: Четыре или восемь высокоскоростных последовательных каналов выделяются разъему XMC P15. Эти линии можно использовать для PCIe (PCI Express), Serial RapidIO или 10 Gigabit Ethernet. Пример проекта будет поддерживать реализацию PCIe Gen 1 с четырьмя или восемью линиями с одним каналом DMA для передачи данных между шиной PCIe и встроенной памятью DDR3.

Восемь или четыре высокоскоростных последовательных канала также выделены для разъема XMC P16. Эти последовательные линии можно использовать для Serial RapidIO, PCIe, Gigabit Ethernet, XAUI или Xilinx Aurora. Пример проекта будет поддерживать двойные интерфейсы Aurora для использования этих дорожек. Два глобальных тактовых сигнала и 34 выбранных сигнала ввода-вывода также будут доступны на разъеме P16. Выбор сигналов ввода-вывода — это контакты ввода-вывода 2,5 В, которые можно выбрать из стандартов несимметричного ввода-вывода (LVCMOS, HSTL и SSTL) и стандартов дифференциального ввода-вывода (LVDS, HT, LVPECL, BLVDS, дифференциальных HSTL и SSTL). ).

Выбор сигналов ввода-вывода — это контакты ввода-вывода 2,5 В, которые можно выбрать из стандартов несимметричного ввода-вывода (LVCMOS, HSTL и SSTL) и стандартов дифференциального ввода-вывода (LVDS, HT, LVPECL, BLVDS, дифференциальных HSTL и SSTL). ).

Разъем ввода-вывода P4 на задней панели обеспечивает две пары глобальных дифференциальных часов и 30 пар сигналов LVDS.

Плата имеет 128 Мб x 64-бит DDR3 SDRAM и 32 Мб x 16-бит параллельную Flash. Параллельная флэш-память обеспечивает хранение как данных конфигурации FPGA, так и памяти программ ЦП MicroBlaze.

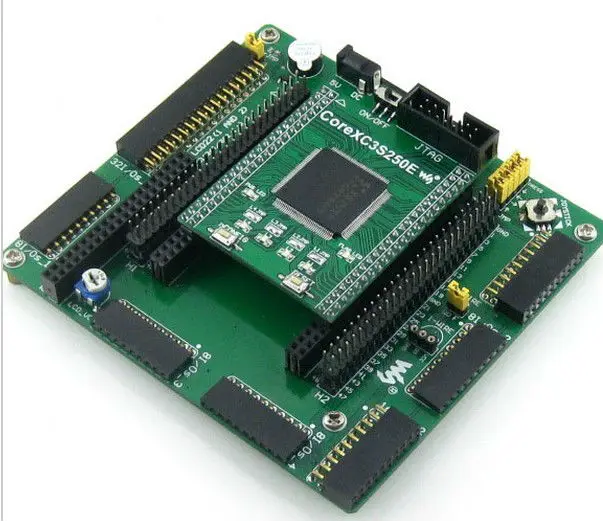

XMC-SLX: плата XMC FPGA с интерфейсом PCIe, подключаемые мезонинные модули расширения ввода-вывода.

PMC-SLX: конфигурируемые пользователем модули Spartan-6 FPGA с подключаемыми модулями ввода/вывода.

Реконфигурируемые модули XMC-SLX и PMC-SLX используют Xilinx Spartan 6 XC6SLX150 FPGA. Реконфигурация ПЛИС возможна путем прямой загрузки в ПЛИС Xilinx по шине PCIe. Кроме того, во встроенную флэш-память можно загрузить данные конфигурации FPGA для автоматической настройки Xilinx при включении питания. Программирование флэш-памяти также осуществляется через шину PCIe. Acromag предоставляет пример конструкции, которая включает в себя интерфейс для пользовательского заднего ввода-вывода и передних разъемов ввода-вывода. Пример проекта также включает интерфейс к SRAM с аппаратной поддержкой прямого доступа к памяти.

Реконфигурация ПЛИС возможна путем прямой загрузки в ПЛИС Xilinx по шине PCIe. Кроме того, во встроенную флэш-память можно загрузить данные конфигурации FPGA для автоматической настройки Xilinx при включении питания. Программирование флэш-памяти также осуществляется через шину PCIe. Acromag предоставляет пример конструкции, которая включает в себя интерфейс для пользовательского заднего ввода-вывода и передних разъемов ввода-вывода. Пример проекта также включает интерфейс к SRAM с аппаратной поддержкой прямого доступа к памяти.

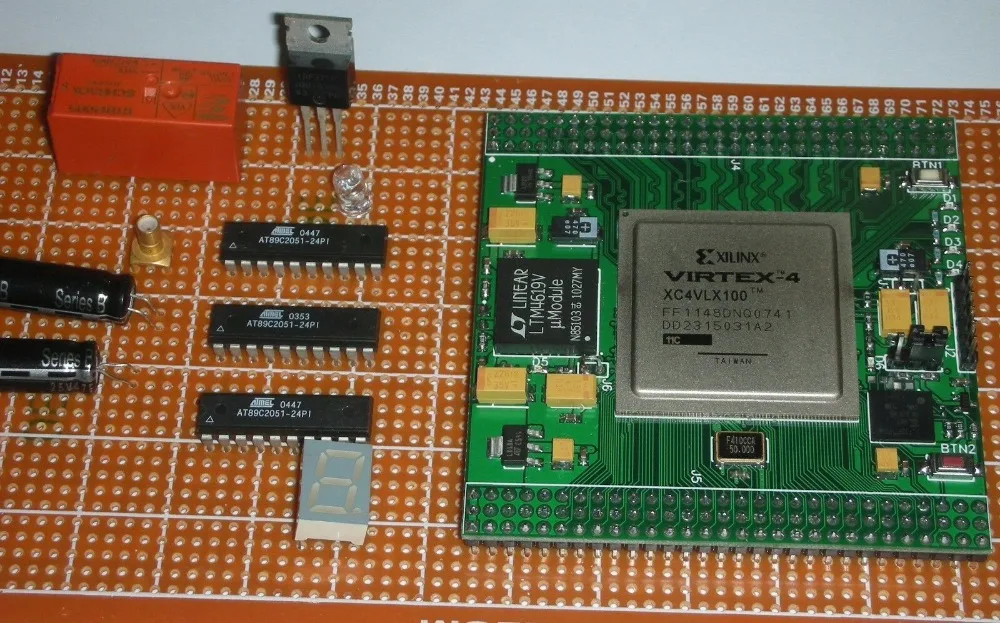

XMC-VLX: плата XMC FPGA с интерфейсом PCIe, подключаемые мезонинные модули расширения ввода-вывода.

PMC-VFX: конфигурируемая пользователем ПЛИС Virtex-5 с подключаемым модулем ввода/вывода .

PMC-VLX: конфигурируемая пользователем ПЛИС Virtex-5 с подключаемым модулем ввода/вывода .

PMC-VSX: Настраиваемая пользователем ПЛИС Virtex-5 с подключаемым модулем ввода/вывода.

Платы Acromag XMC-VLX, PMC-VFX, PMC-VLX и PMC-VSX оснащены реконфигурируемой FPGA Xilinx® Virtex™-5, дополненной несколькими высокоскоростными буферами памяти и высокопроизводительным интерфейсом PCIe. Полевой ввод-вывод взаимодействует с FPGA через разъем J4/P4 на задней панели и/или с дополнительными сменными модулями ввода-вывода AXM на передней панели.

Результатом стал мощный и гибкий модуль процессора ввода-вывода, способный выполнять пользовательские наборы инструкций и алгоритмы.

Три модели обеспечивают выбор ПЛИС с оптимизированной логикой в соответствии с вашими требованиями к производительности. Хотя нет ограничений на использование этих плат, несколько приложений идеальны. Типичные области применения включают аппаратное моделирование, связь, военные серверы, внутрисхемную диагностику, разведку сигналов и обработку изображений.

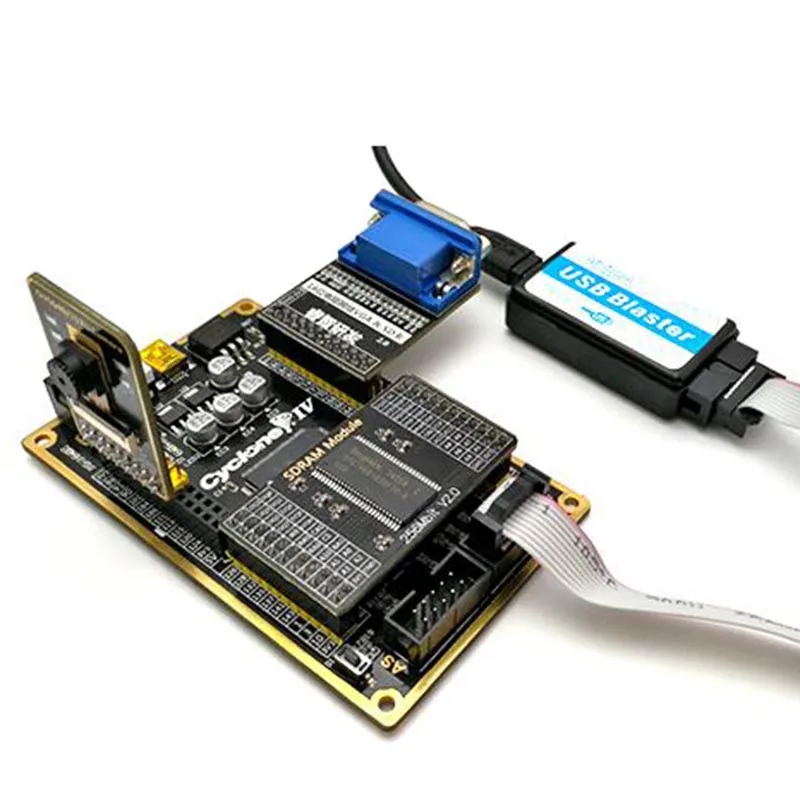

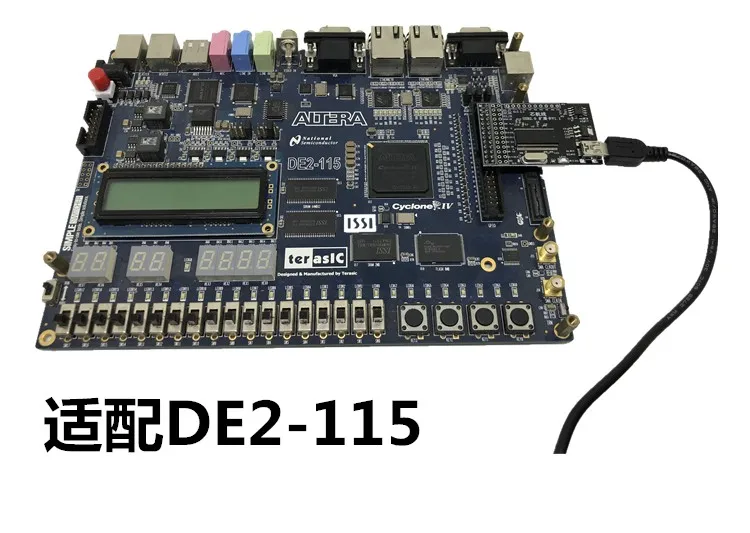

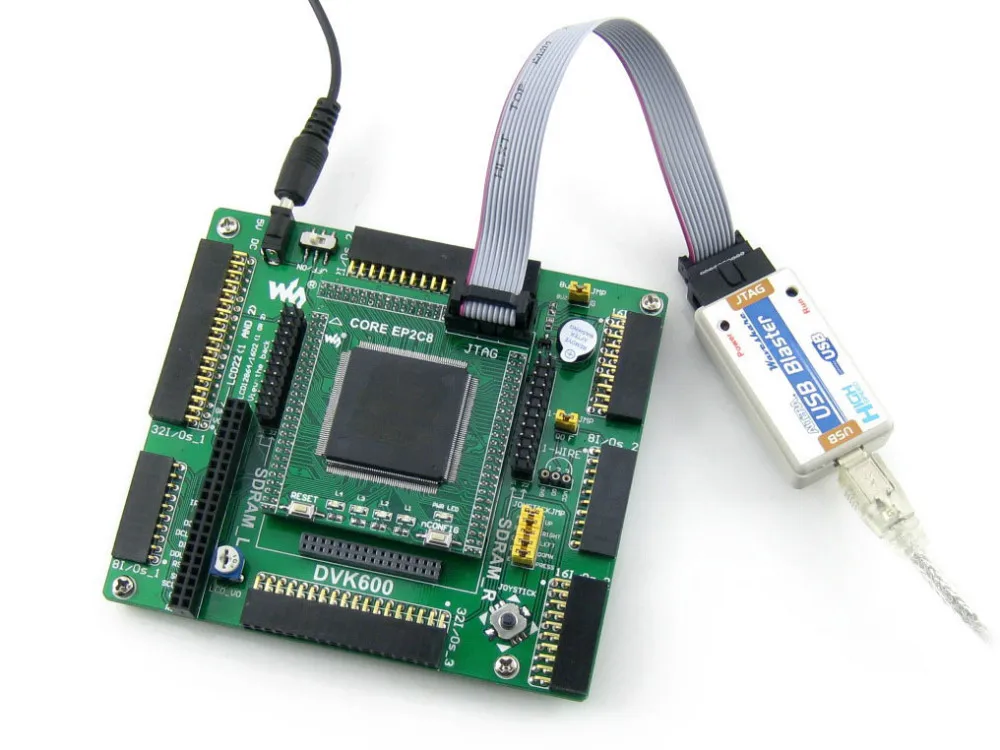

Технологии программируемой логики, такие как программируемые вентильные матрицы (FPGA), являются важным компонентом набора инструментов любого современного схемотехника. Благодаря своим обширным возможностям, уникальным образом подходящим для широкого круга приложений, отладочные платы FPGA идеально подходят для решения многих проблем, стоящих перед быстро развивающимся технологическим сектором. Ключевые преимущества технологий программируемой логики включают в себя огромную гибкость, экономию средств по сравнению с нестандартными микросхемами и повышенную производительность за счет аппаратного параллелизма.

Благодаря своим обширным возможностям, уникальным образом подходящим для широкого круга приложений, отладочные платы FPGA идеально подходят для решения многих проблем, стоящих перед быстро развивающимся технологическим сектором. Ключевые преимущества технологий программируемой логики включают в себя огромную гибкость, экономию средств по сравнению с нестандартными микросхемами и повышенную производительность за счет аппаратного параллелизма.

В мире встраиваемых систем реконфигурируемость FPGA затмевает многие альтернативы. Мы предлагаем что-то для всех, с обилием справочных материалов, поддержки, проектов и документации.

Конкретные приложения, использующие плату FPGA, включают цифровую обработку сигналов, биомедицинские приборы, контроллеры устройств, программно-определяемое радио, случайную логику, медицинскую визуализацию, эмуляцию компьютерного оборудования, распознавание голоса, криптографию, фильтрацию и кодирование связи и многое другое. Приложения бытовой электроники включают смартфоны, автономные транспортные средства, камеры, дисплеи, средства обработки видео и изображений, а также системы безопасности. Платы разработки FPGA также используются для многих коммерческих приложений, таких как серверы, и различных рынков, включая аэрокосмическую и оборонную промышленность, медицинскую электронику и распределенные денежные системы.

Платы разработки FPGA также используются для многих коммерческих приложений, таких как серверы, и различных рынков, включая аэрокосмическую и оборонную промышленность, медицинскую электронику и распределенные денежные системы.

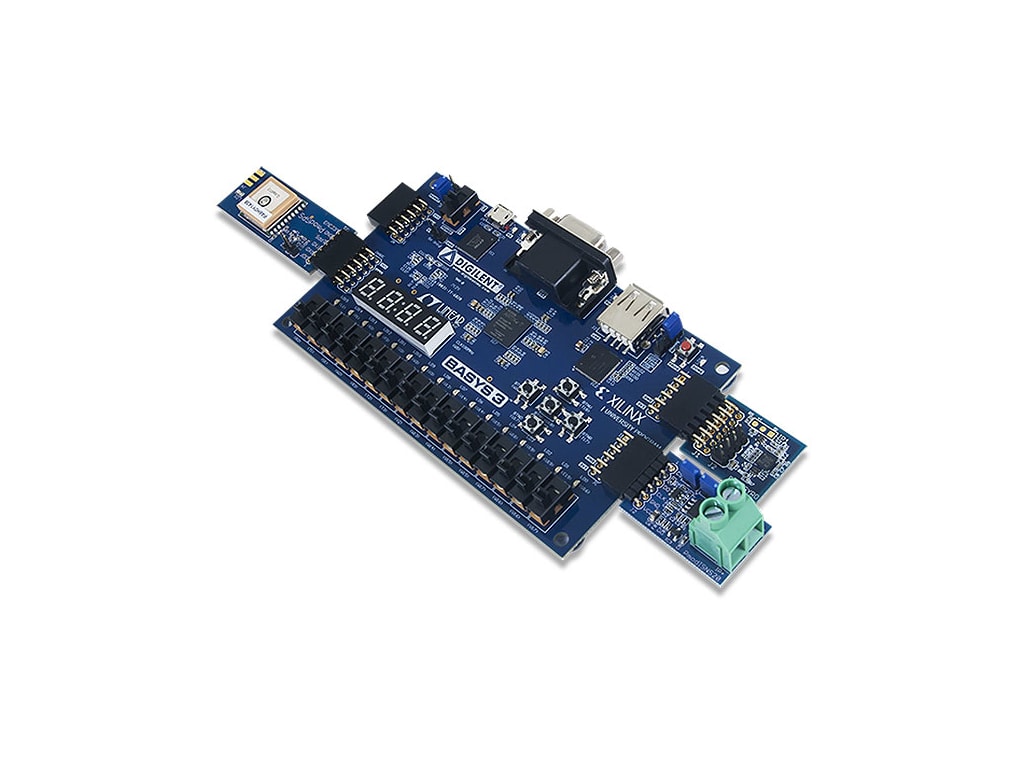

Для новичков, которые только изучают или хотят изучить мир средств разработки FPGA, мы рекомендуем ознакомиться с нашей подборкой вводных досок. Эти платы предназначены для использования без дополнительных аксессуаров или оборудования. У них по-прежнему есть варианты расширения через порты Pmod, а некоторые предоставляют доступ к заголовкам Arduino, что позволяет пользователям создавать более сложные проекты. Наши вводные доски отлично подходят для небольших проектов, где доступность и простота использования являются ключевыми.

Компания Digilent является разработчиком мирового класса карт Xilinx FPGA и системных плат SoC, которые сочетают в себе максимальную производительность с максимальной ценностью. Мы ваш универсальный магазин FPGA с конкурентоспособными ценами на FPGA.