Резюме № 7561201

Инженер разработчик/Программист FPGA, C/ Руководитель инженерной группы / Схемотехник /QA / FAEБыл на этой неделе

По договорённости40 лет (родился 29 июня 1982), не состоит в браке, детей нетСанкт-Петербург, готов к переезду: Москва, Казань, готов к командировкам

Занятость

не указано

Гражданство

Россия

Добавить в избранное

Поделиться

Фото, имя и контакты доступны только авторизованным пользователям

Факультет: Радиотехнический (РТ)

Специальность: Телевидение и Видеотехника (ТВ)

FPGA, Quartus, Qsys, Platform Designer, Signal Tap, In System Memory Content Editor, ModelSim, Altium Disigner, Keil, Verilog, VHDL, C, ПЛИС Имею представление HTML, CSS, Linux, Bash, Shell, Python (CV2, OS, nympy, json, socket), FAE

Добавить в избранное

Поделиться

Фото, имя и контакты доступны только авторизованным пользователям

Похожие резюмеВсе 231 похожее резюме

Обновлено 25 маяВедущий инженер по согласованию, руководитель группы, отдела110 000 ₽

Последнее место работы (6 мес. )Главный специалистНоябрь 2022 – работает сейчасПоказать контакты

)Главный специалистНоябрь 2022 – работает сейчасПоказать контактыДобавить в избранное

Обновлено 3 апреляРуководитель группы, начальник участка, инженерз/п не указана

Последнее место работы (4 года и 8 мес.)Инженер по эксплуатации и ремонтуОктябрь 2018 – работает сейчасПоказать контактыДобавить в избранное

Обновлено вчераИнженер-программист60 000 ₽

Последнее место работы (15 лет и 7 мес.)ИнженерАпрель 2005 – ноябрь 2020Показать контактыДобавить в избранное

Обновлено 21 маяИнженер-программист, информатик, разработчик ПО встраиваемых систем, системный инженер100 000 ₽

Последнее место работы (8 лет и 8 мес.)Инженер-программистОктябрь 2014 – работает сейчасПоказать контактыДобавить в избранное

Обновлено 21 маяИнженер-разработчик РЭС90 000 ₽

Последнее место работы (2 года и 6 мес.)Инженер-разработчик РЭАНоябрь 2020 – работает сейчасПоказать контактыДобавить в избранное

Обновлено 26 маяИнженер-программист контроллеров ARM STM3270 000 ₽

Последнее место работы (10 лет и 4 мес. )Ведущий специалист ИТОктябрь 2008 – февраль 2019Показать контакты

)Ведущий специалист ИТОктябрь 2008 – февраль 2019Показать контактыДобавить в избранное

Обновлено 25 маяКонструктор, инженер-технолог, программист ЧПУ по листовой обработке, авиатехник, начальник отдела148 000 ₽

Последнее место работы (1 год и 7 мес.)Инженер-технолог по кооперацииОктябрь 2021 – работает сейчасПоказать контактыДобавить в избранное

Обновлено 25 маяИнженер-программист 1С80 000 ₽

Последнее место работы (6 лет и 12 мес.)ИнженерИюнь 2016 – работает сейчасПоказать контактыДобавить в избранное

Обновлено 5 маяИнженер-программист250 000 ₽

Последнее место работы (6 лет и 11 мес.)Ведущий электроникИюль 2016 – работает сейчасПоказать контактыДобавить в избранное

Обновлено 5 маяИнженер-программистз/п не указана

Последнее место работы (15 лет и 6 мес.)Инженер по автоматизацииАвгуст 2005 – февраль 2021Показать контактыДобавить в избранное

Работа в Санкт-Петербурге / Резюме / IT, Интернет, связь, телеком / Разработка, программирование / Инженер-программист C/C++

Разработка, программирование

Административная работа, секретариат, АХО

Продажи

Мы используем cookies, чтобы улучшить сайт для вас. Подробнее

Подробнее

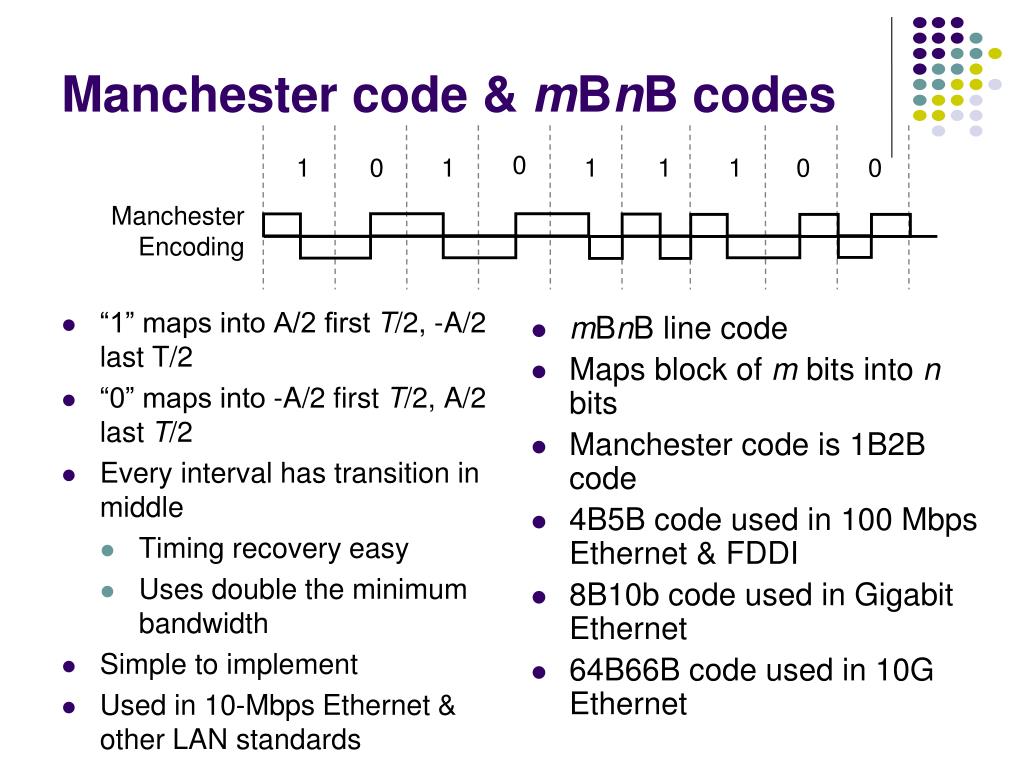

Чтобы понять кодирование/декодирование, настоятельно рекомендуется прочитать о « рабочем несоответствии «.

Обратите внимание, что в следующих таблицах для каждого входного байта A является младшим битом, а H — старшим. Выход получает два дополнительных бита, i и j. Биты передаются от младшего к старшему: a, b, c, d, e, i, f, g, h и j; т.

Остаточное влияние на поток количества передаваемых нулевых и единичных бит сохраняется в виде текущего диспаратности (RD), а эффект нарастания уравновешивается выбором кодирования для следующих символов.

Код 5b/6b представляет собой парный код несоответствия, как и код 3b/4b. Каждое 6- или 4-битное кодовое слово либо имеет одинаковое количество нулей и единиц (несоответствие нулей), либо встречается в паре форм, в одной из которых на два нуля больше, чем единиц (четыре нуля и две единицы, или три нуля и на один соответственно) и один на два меньше. Когда используется 6- или 4-битный код, который имеет ненулевое несоответствие (количество единиц минус количество нулей, т. е. -2 или +2), выбор кодирования положительного или отрицательного несоответствия должен быть таким, который переключает бегущее несоответствие. Другими словами, чередуются ненулевые коды диспаратности.

Детали реализации энкодера ->

Реализация будет основана на LUT, которую можно найти в Спецификации PCIe.

Описание контактов энкодера

Название | Тип | Описание |

Клак | я | Часы энкодера. Этот вывод является основным тактовым сигналом энкодера. Все зарегистрированные входы и выходы энкодера основаны на росте этого Часы. |

РСТН | я | Активный нижний сброс |

Данные_in[7:0] | я | 8-битный ввод данных |

кчар | я | Вход управления |

дисп_в | я | Текущий ввод несоответствия. 0 — -ve несоответствие 1 — +ve несоответствие |

data_out[9:0] | О | Вывод закодированных данных |

дисп_выход | О | Текущий вывод диспаратности |

ошибка | О | Запрошен недопустимый управляющий символ |

————— Конец кода Verilog —————-

Код Verilog для декодера 8b/10b

— ———— Начало кода Verilog —————-

WIP

————— Код Verilog Конец —————-

Тестовый стенд для кода Verilog, созданный кодировщик и декодер.

Спасибо, что посетили Блог, поделитесь своими комментариями.

Ссылка — https://en.wikipedia.org/wiki/8b/10b_encoding

Новое сообщение Старый пост Главная

Подписаться на: Комментарии к сообщениям (Atom)

%PDF-1.7 % 100 0 объект >/OCGs[102 0 R]>>/PageLabels 94 0 R/Страницы 14 0 R/Тип/Каталог>> эндообъект 101 0 объект >/Шрифт>>>/Поля 106 0 R>> эндообъект 99 0 объект >поток приложение/pdf